Emerging digital ICs for power control lack basic features, such as the built-in gate drive and current limiting, that you would normally find in analog ICs. Digital-power controllers generally have only PWM (pulse-width-modulated)-logic output, and discrete gate drivers rarely include current limiting. In addition, most protected FETs work only in low-frequency, low-side applications.

The LM3485 IC from includes high-side gate drive with current limiting (). However, the hysteretic-control scheme of this analog IC is likely to yield questionable performance in some applications due to variable switching frequency and overshoot, as well as an inability to regulate feedback below the 1.24V reference. A traditional PID (proportional-integral-differential)-control scheme can get around these limitations but adds considerable complexity.

The CLZD010 CLOZD (Caldwell-loop-optimization-in-Z-domain) controller-chip IC from both broadens and simplifies control applications though the embedded intelligence of a digital device (). A single time-domain compensator replaces the three frequency-domain PID parameters, eliminating complex stability analysis. The circuit requires no PC interface because you inspect the open-loop response and then use pin settings to configure the closed-loop compensation. However, the PWM output is only a logic-level driver.

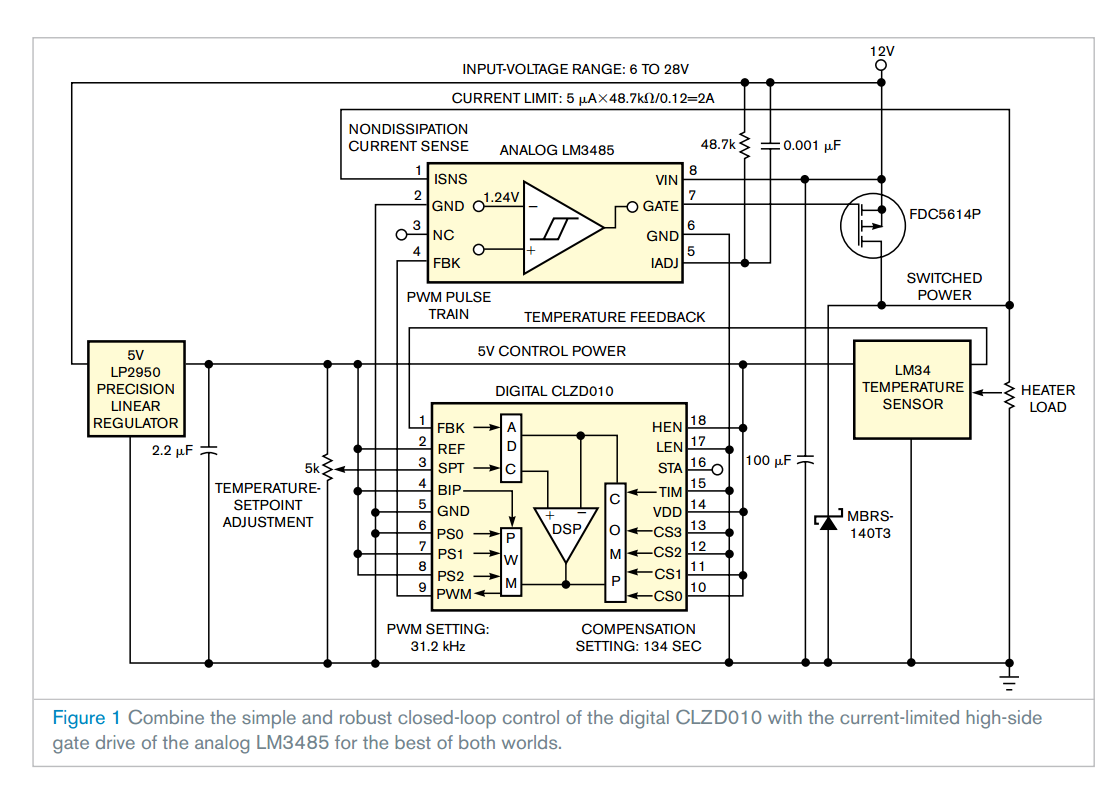

Combine the simple and robust closed-loop control of the digital CLZD010 with the current-limited high-side gate drive of the analog LM3485 for the best of both worlds ().

The PWM-logic level of the digital IC overrides the hysteretic comparator of the analog IC to switch the FET. A second comparator at ISNS, Pin 1 in the LM3485, turns off the FET if the voltage across it exceeds a predetermined value during conduction to limit current.

In the thermal-response example (), the circuit takes about three minutes for the open-loop temperature to reach roughly two-thirds of its final value, so closed-loop compensation, at 134 seconds, is slightly faster in . The resultant closed-loop temperature quickly nears its final value due to maximum drive; voltage then decreases to allow the temperature to settle at the setpoint without overshoot (). You can use this basic circuit combination to satisfy a broad range of applications in multiple industries.